There are some radical changes in HDMI 2.1, the most recent update to the HDMI specification. HDMI 2.1 supports higher video resolutions and faster refresh rates, including 4K 120, 8K 60, and even 10K, as well as Dynamic HDR formats by increasing the cable’s bandwidth from HDMI 2.0’s 18 Gbps up to 48 Gbps and beyond. But what enables HDMI 2.1’s increase in bandwidth and performance?

In this article, I will explain the HDMI 2.1 physical layer changes and compression schemes. I will also detail how to check HDMI 2.1 signal quality.

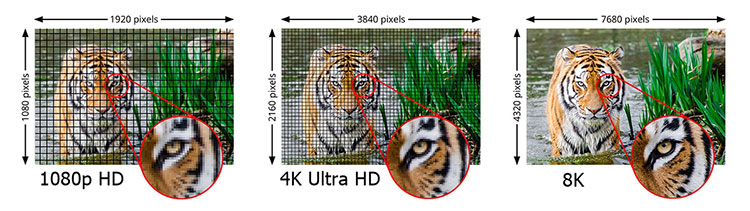

HDMI 2.1 features two times the horizontal and vertical resolutions of 4K. It also offers higher frame rates than past HDMI versions. Support for greater resolutions and frame rates allows HDMI 2.1 to output 4K at 120 Hz, 8K at 60 Hz, and 10K video.

HDMI 2.1 also supports the latest color spaces, such as BT.2020, with 10 or more bits per color and higher frame rates in uncompressed 8K resolution video at 60 frames (4:2:0) per second and 4K video at 120 frames (4:4:4) per second.

Resolutions that use Display Stream Compression (DSC) technology, like 8K at 120 Hz and 10K at 120 Hz, are only available in fixed rate link of bandwidth (FRL) mode. I’ll explain this more in a later section.

Figure 1 -

8K resolution demonstration

www.hdmi.org

Figure 2 -

HDMI 2.1 supported resolutions

www.hdmi.org

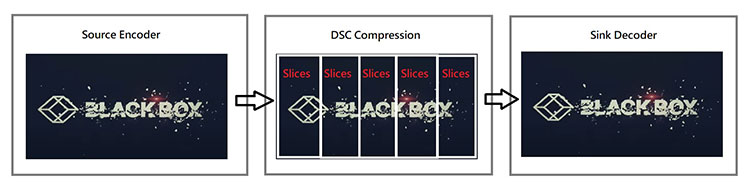

The resolutions marked with an asterisk in Figure 2 use Display Stream Compression. DSC technology transmits the video frame from the source encoder, then the compressed image is split into slices (DSC compressed data). Each slice is an independently encoded partition. After splitting, every slice is decoded at the sink end. Figure 3 explains how DSC works.

Figure 3 -

DSC Compression explanation

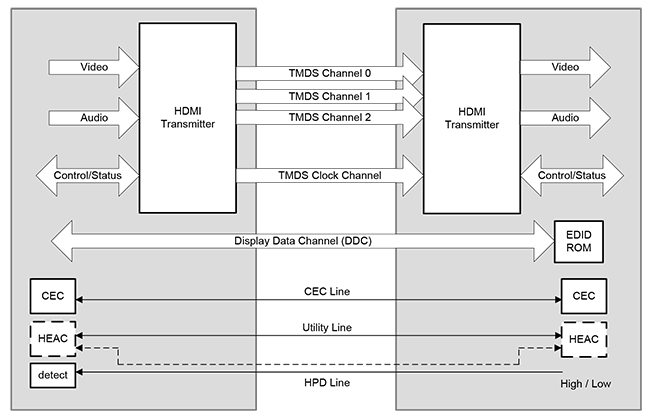

Transition-minimized differential signaling (TMDS) technology is used to transmit high-speed serial data. Silicon Image Inc., a member of the Digital Display Working Group, developed TMDS in 1999. The PanelLink TMDS protocol was first used with DVI, and then it was added to HDMI. Today, HDMI 2.0 and all previous HDMI versions use TMDS. The diagram below shows how HDMI uses TMDS to transmit different types of data.

Figure 4 -

HDMI physical layer block diagram

https://www.ti.com/lit/pdf/slla367

HDMI TMDS uses channels 0 and 1 as well as lanes 2 and 3 to transmit digital audio, video, and auxiliary data. Lane 4 is the TMDS Clock channel that does not transmit any audio, video, or data. TMDS Clock is a frequency reference for data recovery on the three TMDS data channels (channels 0, 1, and 2). This TMDS Clock typically runs at the video pixel rate.

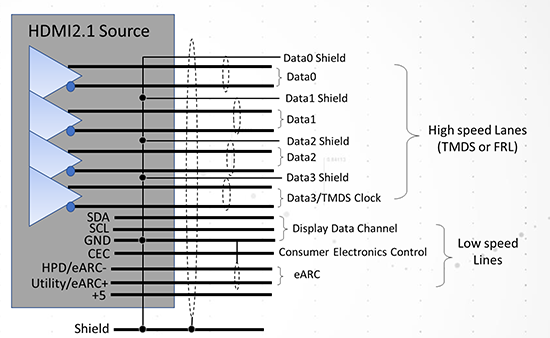

HDMI 2.1 does not use TMDS. It uses the new FRL encoding scheme. Through Link Training, HDMI 2.1’s FRL technology can use three or four lanes at 3 Gbps per lane to 12 Gbps per lane for a maximum composite bit rate of 48 Gbps. TMDS encoding can only use three lanes. HDMI 2.1 is backward compatible with previous HDMI specifications, therefore, FRL has a three lane mode. In table 1, you can see all the bandwidths of FRL lane link rates.

| Table 1 - FRL lane link rates | |||

|---|---|---|---|

| Number of Lanes | Fixed Rate per Lane | Total Bandwidth (Expected) | Max Payload |

| 3 | 3 Gbps | 9 Gbps | 9 Gbps x (16/18) = 8 Gbps |

| 3 | 6 Gbps | 18 Gbps | 18 Gbps x (16/18) = 16 Gbps |

| 4 | 6 Gbps | 24 Gbps | 24 Gbps x (16/18) = 21.33 Gbps |

| 4 | 8 Gbps | 32 Gbps | 32 Gbps x (16/18) = 28.44 Gbps |

| 4 | 10 Gbps | 40 Gbps | 40 Gbps x (16/18) = 35.56 Gbps |

| 4 | 12 Gbps | 48 Gbps | 48 Gbps x (16/18) = 42.67 Gbps |

Figure 5 -

Signal structure of HDMI 2.1 diagram

Keysight Technology

https://www.keysightevent.com/b4

FRL does not require a clock channel like TMDS does. The clock is embedded in the data3 lane (Figure 5), and its information is extracted by clock data recovery (CDR). CDR is the process of extracting timing information from a serial data stream.

Before HDMI 2.1, each TMDS channel ran a 10-bit sequence. TMDS encoding is based on an 8-bit to 10-bit algorithm. This algorithm is only 80% effective because each 10-bit character contains 8 bits of pixel data. The 9th and 10th bits are the only encoding bits.

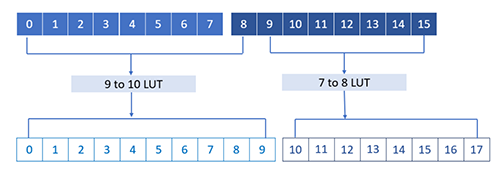

HDMI 2.1 uses 16b/18b FRL encoding that is 88.8% effective. 2.1’s better encoding increases video data throughput 9% over 8b/10b encoding.

Figure 6 -

16b/18b encoding scheme

Granite River Labs

https://graniteriverlabs1-my.sharepoint.com/:b:/g/personal/qanderson_graniteriverlabs_com/Ed3zyf3gv5RLu1ByzSgNcAMBpGezu-WpUkenA7zUQq66iA?e=qxjkLK

Here is a table that lists the differences between HDMI signals:

| Table 2 - HDMI signal summary table | |||||

|---|---|---|---|---|---|

| HDMI Version | |||||

| 1.0–1.2a | 1.3–1.3a | 1.4–1.4b | 2.0–2.0b | 2.1 | |

| Release Date | Dec 2002 (1.0) | Jun 2006 (1.3) | Jun 2009 (1.4) | Sep 2013 (2.0) | Nov-2017 |

| May 2004 (1.1) | Nov 2006 (1.3a) | Mar 2010 (1.4a) | Apr 2015 (2.0a) | ||

| Aug 2005 (1.2) | Oct 2011 (1.4b) | Mar 2016 (2.0b) | |||

| Dec 2005 (1.2a) | |||||

| Signal Specifications | |||||

| Max.Transmission Bit Rate (Gbit/s) | 4.95 | 10.2 | 10.2 | 18 | 48 |

| Max. Data Rate (Gbit/s) | 3.96 | 8.16 | 8.16 | 14.4 | 42.6 |

| Max. TMDS Character Rate (MHz) | 165 | 340 | 340 | 600 | N/A |

| Data Channels | 3 (*) | 3 (*) | 3 (*) | 3 (*) | 4 (**) |

| Encoding Scheme | TMDS 8b/10b | TMDS 8b/10b | TMDS 8b/10b | TMDS 8b/10b | FRL 16b/18b |

| Encoding Efficiency | 80% | 80% | 80% | 80% | 88.80% |

| Compression | - | - | - | - | DSC 1.2 (***) |

| * D0, D1, D2 | |||||

| ** L0, L1, L2, L3 | |||||

| *** HDMI 2.1 incorporates VESA DSC 1.2a link compression. For more information on DSC, click https://www.unigraf.fi/resource/fec-dsc/ | |||||

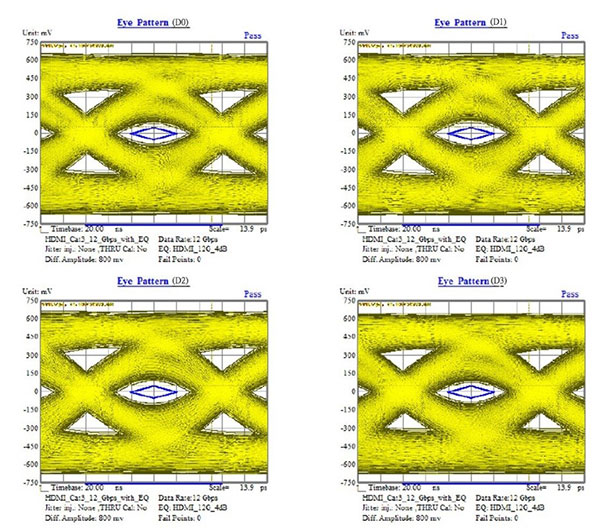

The quality of an HDMI Clock-Data signal can be determined by using a Mask Test. In the Mask Test trace, there should be an open eye shape that avoids the blue eye mask boundary area where signal degradation that can lead to image errors occurs. Take a look at Figure 7 to see the “eye opening,” or region of valid data, that meets the limits of eye opening, as defined in the HDMI 2.1 spec.

Figure 7 -

Data Eye Diagram Test with four lanes at 48 Gbps

The HDMI 2.1 specification is a new architecture that delivers a higher-quality AV experience. The main reason it’s able to output better video than previous specifications is it gets rid of DVI technology to embrace the full four lanes of FRL.

Product Engineer

George Liu has 12 years’ experience in the cabling, data, and video connectivity industry. As a Project and Product Manager at Black Box, he works directly with domestic and international OEM suppliers on new product launches. George is a certified PMP and CQE, and he is a master’s candidate in the industrial management program at National Taiwan University of Science and Technology.